Ttl transistor diagram and gate9/26/2023 Now the output is raised to logic high value. This makes a direct connection between power supply and output terminal. When logic low is applied to either A or B, the corresponding transistor will be turned ON. Operation of a PMOS logic family can be explained by considering a PMOS NAND gate. The structure of PMOS logic can be obtained by replacing NMOS transistors in the CMOS Circuit by a pull down resistor. At the same time, one of the PMOS transistors is ON, so there is connection between output and power supply. This breaks the connection between output terminal and ground. When any of the input is low, either transistor T3 or T4 will be off. Now there is a direct connection between output and ground through transistor T3 and T4. When both inputs of a CMOS NAND gate are at high, then transistors T1, T2 will be ON and transistors T3, T4 will be OFF. So in both states, there is no direct connection between power supply and ground, thereby reducing static power loss of a transistor. Figure shown below is a CMOS inverter.ĭepending on the input value, only one transistor of the CMOS inverter will be ON at a time. CMOS (Complementary Metal Oxide Semiconductor) has complementary and symmetrical NMOS and PMOS transistors. Because of its large power consumption and high requirement of silicon area, CMOS logic gates are preferred over ECL logic families in large scale integrated circuits.īecause of high noise immunity and low static power dissipation, now CMOS logic families is most preferred in large scale integrated circuits. ECL logic families requires large currents therefore power dissipation is 3 to 10 times higher than that of TTL logic families. But the disadvantage of ECL logic families is that it uses a negative power supply such that the logic levels are not compatible with any other logic family and makes analysis and measurement inconvenient. Propagation time for an ECL gate is 0.5 to 2ns, which is very less when compared to its TTL counterpart. This improves the speed of operation at the expense of noise margin. In the active region, charge stored in the base region of transistors is kept to minimum.ĭifference between these two logic states is very small. For logic one it is -0.9 and for logic zero, it is -1.75v. This is achieved by using voltage values close to each other. Transistors are driven either in cut off or in active region. Transistors are not allowed to go into deep saturation thus, eliminating storage delays like in TTL logic families. Emitter Coupled Logic (ECL)Įmitter Coupled Logic (ECL), also referred to as Current Mode Logic families, is a digital technology with extremely high-speed. Now no current reaches the base terminal of the output transistor, so output remains at high state. When any one of the input terminal is low, the current through other branch flows out through this terminal. This current reaches base of the output transistor, allowing it to conduct and pulling down the output voltage to zero. In reverse active mode, less magnitude current flows in the opposite direction. When the two emitters of the input transistors are connected to high voltage, then emitter-base junction of the transistor is reverse biased that means, transistor is in reverse active mode. Function of a multi-emitter transistor is same as that of a two parallel transistor with common base and collector terminals. There are two transistor stages in the circuit, a multi-emitter input transistor and output transistor. Two input NAND gate using TTLįigure shows TTL NAND gate.

Advantages of the TTL logic families include high switching speed (125 MHz), less noise and more current (3 mA) driving capability. In TTL logic family, analog value from 0 V to 0.8 V is logic 0 and 2 V to 5 V is logic 1. For logic gate built using TTL logic families, input are given to the emitters of the input transistor. Using TTL logic families, many logic gates can be fabricated in a single integrated circuit.

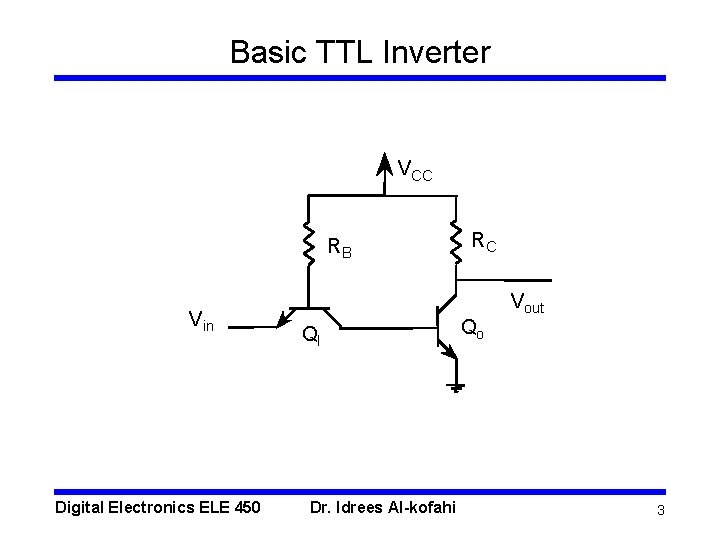

The term transistor-transistor is because both logic function and amplification is done by transistor. In transistor-transistor logic (TTL), logic gates and other digital circuits are made using bipolar junction transistors and resistors. Power: When a circuit switches from one state to the other, power dissipates. Noise Immunity: Maximum noise that a circuit can withstand without affecting the output. Speed: Speed of a logic circuit is determined by the time between the application of input and change in the output of the circuit.įan-in: It determines the number of inputs the logic gate can handle.įan-out: Determines the number of circuits that a gate can drive. The main characteristics of Logic families include: Logic Families indicate the type of logic circuit used in the IC.

0 Comments

Leave a Reply.AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed